Difference between revisions of "RK3328"

From Rockchip open source Document

| (49 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

| + | {{Infobox SoC | ||

| + | | title = RK3328 | ||

| + | | image = [[File:rk3328_soc.png|250px]] | ||

| + | | manufacturer = Rockchip | ||

| + | | process = 28nm | ||

| + | | cpu = Quad-Core ARM Cortex-A53 | ||

| + | | ltwo = | ||

| + | | extensions = | ||

| + | | memory = DDR3/DDR3L/LPDDR3/DDR4 | ||

| + | | gpu = Mali-450MP4 | ||

| + | | vpu = 4K VP9 and 4K 10bits H265/H264 video decode, up to 60fps | ||

| + | | apu = | ||

| + | | video = HDMI 2.0a, | ||

| + | | audio = 8 channels I2S/PDM | ||

| + | | storage = 4x SD Card, eMMC | ||

| + | | usb = 1* USB2.0 otg, 1* USB 2.0 Host, 1* USB 3.0 Host | ||

| + | | other = | ||

| + | | release_date = December 2016 | ||

| + | | website = http://www.rock-chips.com/a/en/products/RK33_Series/2017/0118/829.html | Product Page | ||

| + | }} | ||

| + | | ||

| − | + | | |

| − | |||

| − | |||

| − | |||

= Overview = | = Overview = | ||

| Line 14: | Line 32: | ||

Quad-core Cortex-A53 is integrated with separate Neon and FPU coprocessor, also with shared L2 Cache. | Quad-core Cortex-A53 is integrated with separate Neon and FPU coprocessor, also with shared L2 Cache. | ||

| + | |||

| + | [[File:3328.png|RTENOTITLE]] | ||

= RK3328 SoC Features = | = RK3328 SoC Features = | ||

| + | {| border="0" cellpadding="1" cellspacing="1" style="width: 972px;" | ||

| + | |- | ||

| + | | style="width: 530px;" | | ||

*CPU: | *CPU: | ||

| − | **ARM Cortex-A53 Quad-Core | + | **ARM Cortex-A53 Quad-Core |

| + | **32KB L1 I cache and D cache for each CPU | ||

| + | **256KB L2 cache | ||

| + | *Internal SRAM | ||

| + | **32KB total | ||

*GPU | *GPU | ||

| − | ** Mali- | + | ** Mali-450MP2 |

**Comply with Open GL ES1.1/2.0 | **Comply with Open GL ES1.1/2.0 | ||

*Multi-Media: | *Multi-Media: | ||

| Line 38: | Line 65: | ||

**100M Ethernet w/ built-in PHY | **100M Ethernet w/ built-in PHY | ||

**Built-in CVBS and audio DAC | **Built-in CVBS and audio DAC | ||

| − | **8 channels I2S IO and 8 chanel digital PDM input (for MIC array) | + | **8 channels I2S IO and 8 chanel digital PDM input (for MIC array) |

| − | = | + | | style="width: 429px;" | |

| + | |} | ||

| | ||

| − | |||

| − | |||

= Documentation = | = Documentation = | ||

| − | + | #[http://opensource.rock-chips.com/images/d/d7/Rockchip_RK3328_Datasheet_V1.1-20170309.pdf Rockchip_RK3328_Datasheet_V1.1-20170309.pdf] | |

| − | + | #[http://opensource.rock-chips.com/images/d/d5/RK3328_Linux-Debian_V1.1_Development_Guide-20170711.pdf RK3328_Linux-Debian_V1.1_Development_Guide-20170711.pdf] | |

| − | [[Media: | + | #[[Media:Rockchip_RK3328TRM_V1.1-Part1-20170321.pdf|Rockchip RK3328TRM V1.1-Part1-20170321.pdf]] |

| − | + | #[[Media:Rk3328_hardware_reference.zip|Rk3328 hardware reference.zip]] | |

| − | |||

| | ||

| Line 58: | Line 83: | ||

= Software = | = Software = | ||

| + | See [http://opensource.rock-chips.com/wiki_Linux_user_guide Linux User Guide] setup LInux OS generally; | ||

| − | + | See [http://opensource.rock-chips.com/wiki_U-Boot U-Boot] guide to develop U-Boot; | |

| − | + | See [http://opensource.rock-chips.com/wiki_Rockchip_Kernel Rockchip kernel] to develop kernel; | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | | + | See [http://opensource.rock-chips.com/wiki_Buildroot buildroot and] [http://opensource.rock-chips.com/wiki_Debian debian to] develop and rootfs. |

| | ||

| Line 80: | Line 95: | ||

== Chip configuration == | == Chip configuration == | ||

| − | {| border="1" cellpadding="1" cellspacing="1" | + | {| border="1" cellpadding="1" cellspacing="1" class="table_style" |

|- | |- | ||

| − | + | ! '''chip''' | |

| − | + | ! '''Kernel eMMC index''' | |

| − | + | ! '''Kernel SD index''' | |

| − | + | ! '''Uboot eMMC index''' | |

| − | + | ! '''Uboot SD index''' | |

| − | + | ! '''Baud speed''' | |

|- | |- | ||

| − | | | + | | RK3328 |

| − | | | + | | 2 |

| 0 | | 0 | ||

| 0 | | 0 | ||

| Line 96: | Line 111: | ||

| 1500000 | | 1500000 | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

= References = | = References = | ||

| − | 1.https://en.wikipedia.org/wiki/ARM_Cortex-A53 | + | 1.[https://en.wikipedia.org/wiki/ARM_Cortex-A53 https://en.wikipedia.org/wiki/ARM_Cortex-A53] |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| | ||

Latest revision as of 09:38, 23 March 2022

Contents

Overview

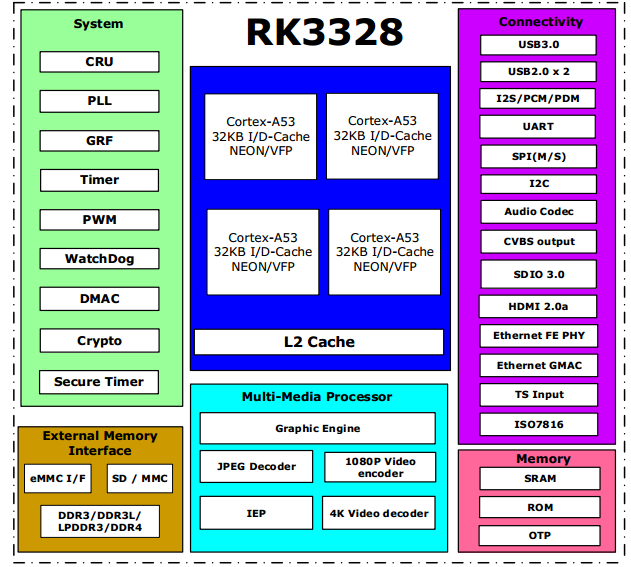

RK3328 offers a high-integration and power efficiency SOC for 4K HDR OTT/IPTV. It support HDR10 ,HLG HDR , 4K 10bits 30fps H.264 video decoder and 4K 10bits 60fps H265 video decoder.Comply with lots of high-performance interface,such as multi-channel display with HDMI2.0a, TV Encoder, the Quad-core GPU can acheive high-resolution display and game.

Cortex-A53

Quad-core Cortex-A53 is integrated with separate Neon and FPU coprocessor, also with shared L2 Cache.

RK3328 SoC Features

|

Documentation

- Rockchip_RK3328_Datasheet_V1.1-20170309.pdf

- RK3328_Linux-Debian_V1.1_Development_Guide-20170711.pdf

- Rockchip RK3328TRM V1.1-Part1-20170321.pdf

- Rk3328 hardware reference.zip

Software

See Linux User Guide setup LInux OS generally;

See U-Boot guide to develop U-Boot;

See Rockchip kernel to develop kernel;

See buildroot and debian to develop and rootfs.

Chip configuration

| chip | Kernel eMMC index | Kernel SD index | Uboot eMMC index | Uboot SD index | Baud speed |

|---|---|---|---|---|---|

| RK3328 | 2 | 0 | 0 | 1 | 1500000 |

References

1.https://en.wikipedia.org/wiki/ARM_Cortex-A53